#### **FRESH** ideas

Wayne Luk Imperial College London

FRESH 11 July 2016 Event Sponsor: Maxeler Technologies

1

## Why FRESH?

- most conferences

- major: past achievements

- minor: future work

- FRESH

- minor: past achievements

- major: future work

- why now?

- 2 FRESH: the Future of REconfigurable Systems and their High-level design

## Time for FRESH ideas!

- it has been a while

- Estrin 1960

- 2015: 25 years of FPL

- 2017: 25 years of FPGA/FCCM

- 2016: 30 years of ASAP

- recent industrial developments

- JP Morgan, CME, Juniper... adopted Maxeler systems

- Microsoft adopted FPGAs in datacentres

- Intel bought Altera

#### Strategic Combination Creates Significant Value

| Product<br>Synergies                 | <ul> <li>Addresses emerging customer workloads in the ~\$37B data center logic market segment</li> <li>New IoT products expected to expand serviceable market by ~\$11B</li> <li>Expected to be ~60% of total value created</li> </ul>         |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cost &<br>Manufacturing<br>Synergies | <ul> <li>OpEx reductions which increase over time</li> <li>Manufacturing leadership which is expected to improve existing<br/>Altera product portfolio and market segment share</li> <li>Expected to be ~40% of total value created</li> </ul> |

#### Expected to be Accretive to Non-GAAP EPS & Free Cash Flow in the First Year After Close

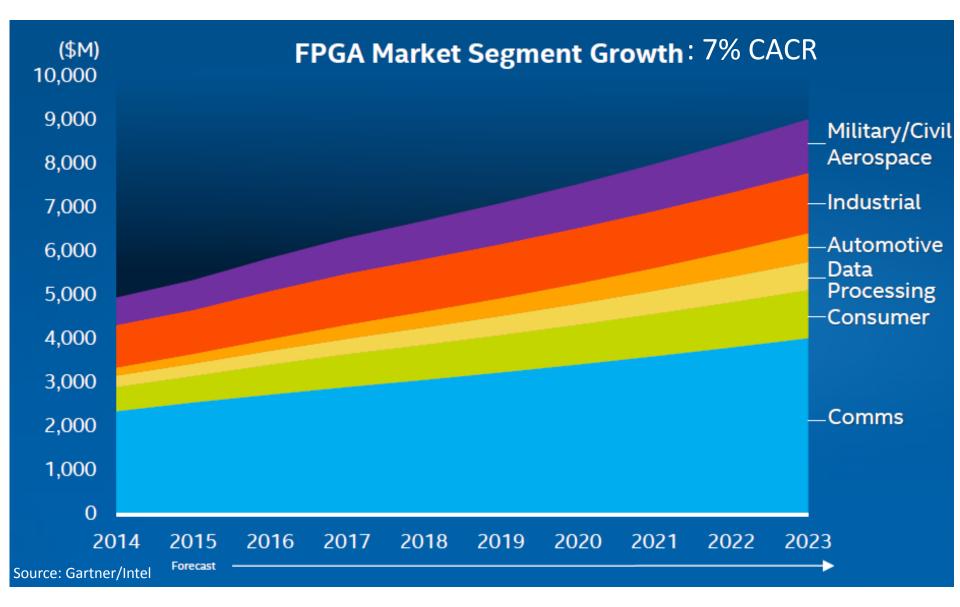

#### Cloud Example: Data Center FPGA Acceleration Up to 1/3 of Cloud Service Provider Nodes to Use FPGAs by 2020

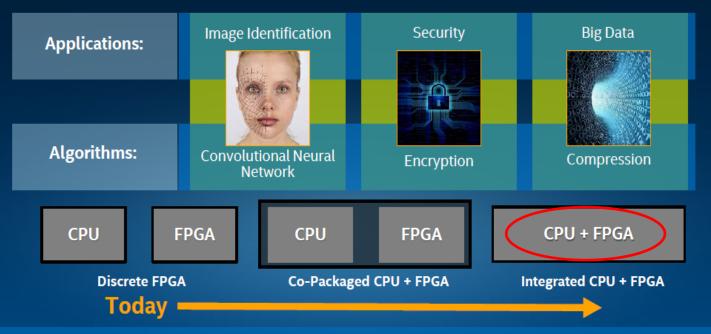

>2X performance increase through integration

Reduces total cost of ownership (TCO) by using standard server infrastructure Increases flexibility by allowing for rapid implementation of customer IP and algorithms

#### Industrial Automation Control Pre-Programmed (ASSP replacement)

Processor, mem controller, security, standard IO

Industrial Specific Real-time control and acceleration

One Silicon Design

**Base IA Complex**

FPGA

#### Integrated die and multi-chip packages

Advanced Driver Assistance Systems Customer Defined IP (ASIC replacement)

Processor, mem controller, security, standard IO

Automotive Specific Functional Safety, Computer Vision, Proprietary Acceleration

#### IoT Application Examples

- Integrated solutions accelerate growth in key IoT segments by adding new functionality, improving performance, and lowering cost

- ~\$11B incremental SAM by 2020 as integrated FPGAs become cost competitive with ASICs & ASSPs

- Customers can program their own IP, replacing ASICs

- Intel can pre-program industry-specific IP, replacing ASSPs

- Expected to reduce time-to-market by more than 50%

# Why fundamental?

• conventional computing: fit program to processor

reconfigurable/custom computing: fit processor to program

reconfigurable fabric: heterogeneous programmable resources

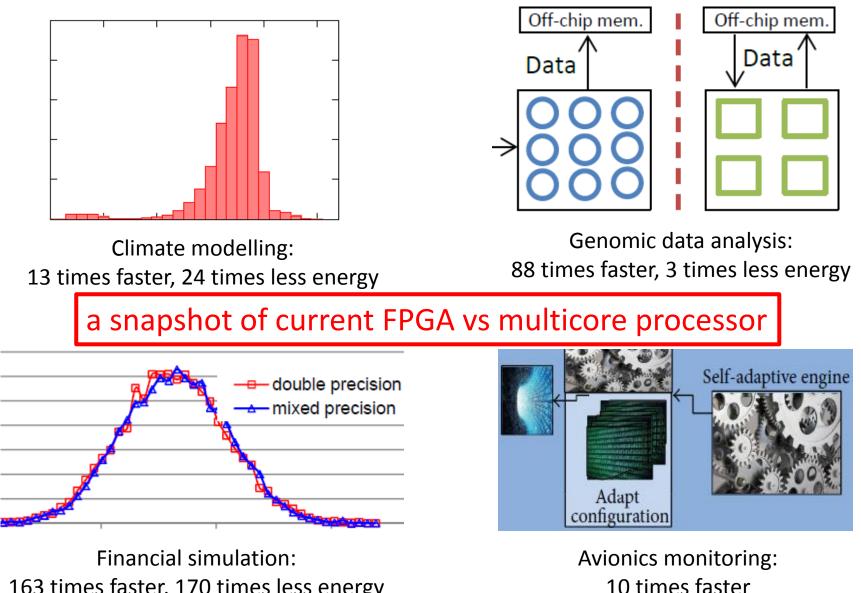

## Reconfigurable acceleration: examples

163 times faster, 170 times less energy

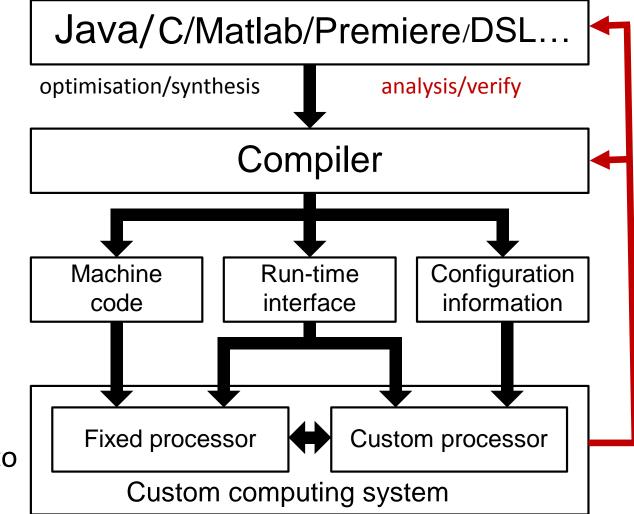

# Vision: customise synthesis + analysis

application description

partition, compile, analysis, verify

system-specific programming interface

system-specific adaptation: clouds to devices

#### Future: short term

- accelerators for cloud computing

- virtualisation + elastic resource model + event-triggering

POETS project

- automate compilation and run-time reconfiguration

- mixed precision + type/aspect-driven + exa-scale systems

TYTRA project

EXTRA project

- reconfigurable fabric: memory + Sys/Net-OC architecture

- optimised: dynamic data access, heterogeneous resources...

- machine learning and reconfigurable design

- reconfigurable design accelerates machine learning + vice versa

- self-adaptive design and auto-tuning

- functional/temporal/statistical assertions, on-line optimisation

# Future: long term

- fundamental, timeless principles

- models: fabric + systems

- mapping from high-level: correct + efficient

- automation: specialisation + generalisation

- limits: how far away from ideal

- understanding trade-offs

overlay

- automation: quality <u>vs</u> tool runtime/resources/user guide privacy, resilience

- speed <u>vs</u> resources <u>vs</u> energy <u>vs</u> accuracy <u>vs</u> security...

- optimisation: compile-time vs run-time

- technologies: silicon vs molecular vs quantum vs optic...

- grand challenges for the next industrial revolution?

# FRESH: why here

- most UK research teams on reconfigurable systems

- industry: Maxeler

- rest of the world: Toronto

- audience: Europe + Asia

- research areas

- cover most areas

- complementary

- mutual respect

- opportunity and challenge: cross fertilisation

- what can we do together?

- what can we share?

#### Discussions

- how to accelerate advances in

- reconfigurable systems

- related technologies

- how to promote sharing of resources for

- research and teaching

- hardware, software, application data...

- how to improve interactions between

- universities

- industry

- funding agencies

#### Next

- The Future of Reconfigurable Systems: an Industrial Perspective

- Overlays: a Solution Paradigm for FPGA High-Level Design?

- Architecture Centric Overlays for Abstraction and Performance

- break

- New Vistas in High Level Synthesis

- FPGA Virtualization for Enabling General Purpose Reconfigurable Computing

- Reconfigurable Market-on-Chip

- \* lunch

#### Next

- The Future of Reconfigurable Systems: an Industrial Perspective

- Overlays: a Solution Paradigm for FPGA High-Level Design?

- Architecture Centric Overlays for Abstraction and Performance

- New Vistas in High Level Synthesis

- FPGA Virtualization for Enabling General Purpose Reconfigurable Computing

- Reconfigurable Market-on-Chip

- Heterogeneous Dataflow for Heterogeneous MPSoC FPGA

- Communication as a first class design constraint for reconfigurable systems

- Computing to the Energy and Performance Limits in Heterogeneous CPU-FPGA Devices

- High-Level Programming of FPGAs using Type-Driven Program

<sup>16</sup> Transformations and Cost-Modelling \* Break; Discussion + Wrap-Up